A User Manual

on

# **8085 Simulator**

https://8085Simulator.github.io

https://8085simulator.codeplex.com

Product Version 2.0 STABLE RELEASE

By JUBIN MITRA

March 1, 2018

# **Version and Bug fixes**

## **Release Date**

| Version Release Date                         | Download Link                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|----------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Version 1Release DateVersion 110th Oct, 2009 | https://github.com/8085simulator/8085simulator/blob/master/8085Compiler_v0.jar         8085 Simulator         Ele Tools Settings Simulation Load Sample Program Help         6005 Assembly Language Editor         Register S:         Memory Editor         Register C       00 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                                              | Fina Restart       00       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       0       < |

Version 2 1<sup>st</sup> Jun, 2014 https://github.com/8085simulator/8085simulator/blob/master/8085Compiler\_v1.jar

| 🖢 8085 Simu                                                            | ilator                                                                                                                                                                                                                                                                       |                       |            |           |      | -         |           | ×         |

|------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|------------|-----------|------|-----------|-----------|-----------|

| ile Edit Tools Settings Simulation Subroutine View Load Sample Program | Help                                                                                                                                                                                                                                                                         |                       |            |           |      |           |           |           |

| Editor Assembler                                                       | Registers Memory                                                                                                                                                                                                                                                             | Devices               |            |           |      |           |           |           |

| 8085 Assembly Language Editor                                          | Registers :                                                                                                                                                                                                                                                                  |                       |            |           |      |           |           |           |

| Assembler Disassembler                                                 | Register                                                                                                                                                                                                                                                                     | Value                 | 7 6        | 5         | 4    | 3         | 2 1       | 0         |

|                                                                        | Accumulator                                                                                                                                                                                                                                                                  | 00                    | 0 0        | 0         | 0    | 0         | 0 0       | 0         |

|                                                                        | Register B                                                                                                                                                                                                                                                                   |                       | 0 0        | 0         | 0    | 0         | 0 0       |           |

|                                                                        | Register C                                                                                                                                                                                                                                                                   |                       | 0 0        | 0         | 0    | 0         | 0 0       | -         |

|                                                                        | Register D                                                                                                                                                                                                                                                                   |                       | 0 0        | 0         | 0    | 0         | 0 0       |           |

|                                                                        | Register E                                                                                                                                                                                                                                                                   |                       | 0 0        | 0         | 0    | 0         | 0 0       |           |

|                                                                        | Register H                                                                                                                                                                                                                                                                   |                       | 0 0        | 0         | 0    | 0         | 0 0       |           |

|                                                                        | Register L                                                                                                                                                                                                                                                                   |                       | 0 0        | 0         | 0    | 0         | 0 0       | -         |

|                                                                        | Memory(M)                                                                                                                                                                                                                                                                    |                       | 0 0        | 0         | 0    | 0         | 0 0       |           |

|                                                                        | Tienory(T)                                                                                                                                                                                                                                                                   | 00                    |            | v         | •    | v         | 0 0       |           |

|                                                                        | Resister                                                                                                                                                                                                                                                                     | Value                 | s z        | *         | AC   | *         | P *       | CY        |

|                                                                        | Flag Resister                                                                                                                                                                                                                                                                | 00                    | 0 0        | 0         | 0    | 0         | 0 0       | 0         |

|                                                                        | Type         Type           Stack Pointer(SP)         000           Memory Pointer (HL)         000           Program Status Word(PSW)         000           Program Counter(PC)         000           Clock Cycle Counter         0           Instruction Counter         0 |                       |            |           |      |           |           |           |

|                                                                        | SOD SID                                                                                                                                                                                                                                                                      | INTR TRAF             |            | 87.5<br>0 |      | R6.5<br>0 |           | ₹5.5<br>0 |

|                                                                        | For SIM instruction                                                                                                                                                                                                                                                          | SOD SDE *             | R7         |           | SE I | M7.5<br>0 | M6.5<br>0 | M5.5<br>0 |

| Autocorrect Assemble                                                   | For RIM instruction                                                                                                                                                                                                                                                          | SID 17.5 16.<br>0 0 0 | 5 I5.<br>0 |           | E I  | M7.5<br>0 | M6.5<br>0 | M5.5<br>0 |

|                                                                        | No. Converter Tool : -                                                                                                                                                                                                                                                       |                       |            |           |      |           |           |           |

|                                                                        | Hexadecimal                                                                                                                                                                                                                                                                  | Decim                 | al         |           | _    | Bi        | narv      |           |

|                                                                        | 0                                                                                                                                                                                                                                                                            |                       |            | 0         |      |           | ,         | 0         |

| Created by : Jubin Mitra                                               |                                                                                                                                                                                                                                                                              |                       |            |           | -    | -         |           |           |

## **Bug fixes**

From the 2nd Version of this software bug history log is maintained.

# Preface

This software was first published in October 10, 2009 and since then it has been in this field. It is gratifying to see such acceptance and popularity of the software in many institutes and universities. This tool is an integrated software environment for teaching microprocessor concepts. The second version of the software has undergone many changes and bug fixing.

### **Migration Notice**

This is to bring to the notice of the users that the previously popular site http://8085simulator. codeplex.com has been migrated to https://8085Simulator.github.io. Everything remained the same. Hope it would be of not much trouble for the users. The design still maintains the same simplicity and maintained under the open source license GPL v2.

### About the Author

Author has completed his B.Tech. in Electronics and Communication Engineering from Heritage Institute of Technology, Kolkata and M.E. from Bengal Engineering and Science University (BESU), Howrah, India. He is currently pursuing Ph.D. at Variable Energy Cyclotron Centre (VECC) at Kolkata under the aegis of Homi Bhabha National Institute (HBNI).

### Acknowledgment

My sincere thanks and love for my parents Dipendra Kali Mitra and Bharati Mitra for their continuous inspiration, encouragement, love, patience and support during this software development.

This software was designed during my B.Tech days when I was studying 8085 Microprocessor subject itself. Since then it has evolved and attained much maturity. I would do injustice if I do not mention the name of my friend circle, who always maintained a positive vibe and joyous environment for creative work culture. Cheers to my college friends Anirban Goswami, Debanjan Chatterjee and Abhyuday Jatty.

I salute the spontaneous guidance and inspiration of my college faculty members Amitava Hatial, Saibal Dutta, and Surajit Bagchi.

### **Contact Details**

In the end I would love to request my esteemed users to kindly send their valuable suggestions for the improvement of the software and to notify me any errors that you may come across while using the software. You can comment in the blogspot http://8085simulatorj.blogspot.in. If you need to contact me directly just drop a mail in my mailbox, jm61288@gmail.com. If it is applicable for all users then I would suggest you to post it in the blogspot, so that it is accessible to other users as well.

# Contents

| 1 | Proc | duct Description                                                       | 5  |

|---|------|------------------------------------------------------------------------|----|

|   | 1.1  | Motivation                                                             | 5  |

|   | 1.2  | Installation and Upgrade Note                                          | 5  |

|   | 1.3  | Limitations                                                            | 5  |

|   | 1.4  | Known Issues                                                           | 6  |

|   | 1.5  | Software Design Architecture                                           | 6  |

|   |      | 1.5.1 Preprocessor                                                     | 6  |

|   |      | 1.5.2 Assembler                                                        | 6  |

|   |      | 1.5.3 Simulator Engine                                                 | 7  |

|   |      | 1.5.4 Step-wise Traversal Controller                                   | 7  |

|   | 1.6  | Source Code                                                            | 7  |

| 2 | Feat | tures                                                                  | 8  |

| 3 | Con  | nparitive Analysis                                                     | 11 |

| 4 | Asse | embler Directives                                                      | 12 |

|   | 4.1  | Directives                                                             | 12 |

|   | 4.2  | Number Format Support                                                  | 13 |

|   |      |                                                                        |    |

| 5 | Disa | ssembler                                                               | 14 |

|   | 5.1  | Disassembler Demonstration                                             | 14 |

|   | 5.2  | Intel HEX                                                              | 16 |

|   | 5.3  | Writing Hexcode in Disassembler                                        | 17 |

|   |      | 5.3.1 Limitation of disassembler                                       | 17 |

| 6 | Tim  | ing Diagram generator                                                  | 18 |

|   | 6.1  | Static Timing Diagram Generation                                       | 19 |

|   | 6.2  | Dynamic Timing Diagram Generation By Manual Step by Step Simulation    | 20 |

|   | 6.3  | Dynamic Timing Diagram Generation By Automatic Step by Step Simulation | 21 |

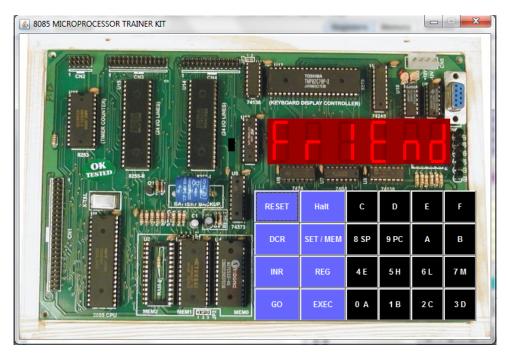

| 7 | Trai | iner Kit Emulator                                                      | 22 |

|   | 7.1  | Keyboard                                                               | 22 |

|   | 7.2  | Using the Trainer Kit Emulator                                         | 23 |

|   |      | 7.2.1 How to enter a program                                           | 23 |

|   |      | 7.2.2 To Execute the Program                                           | 23 |

|   |      | 7.2.3 How to examine memory and register contents                      | 23 |

|   | 7.3  | Shortcut Keys for Trainer Kit Button                                   | 26 |

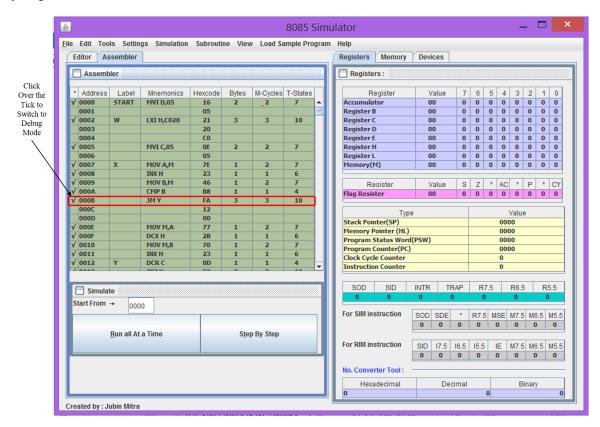

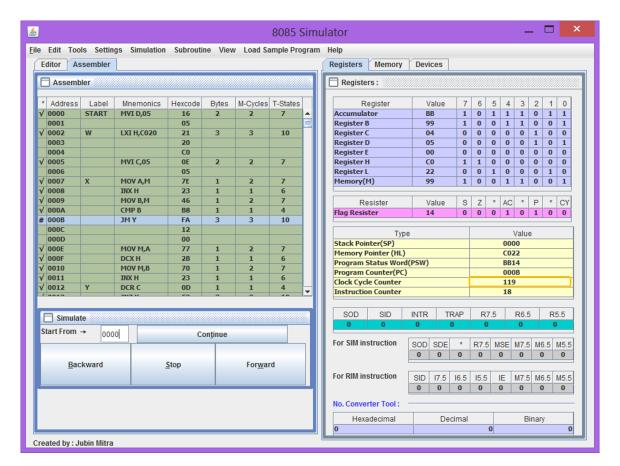

| 8 | Deb  | ugging Mode                                                            | 27 |

|   |      |                                                                        |    |

| 9 | Tool | IS                                           | 30 |

|---|------|----------------------------------------------|----|

|   | 9.1  | Insert Delay Subroutine                      | 31 |

|   |      | 9.1.1 Working Example of a delay sub-routine | 32 |

|   | 9.2  | Interrupt Service Subroutine                 | 33 |

|   | 9.3  | Number Conversion Tool                       | 34 |

## **License and Disclaimer**

### **GNU General Public License version 2 (GPLv2)**

Copyright (C) 1989, 1991 Free Software Foundation, Inc. 59 Temple Place, Suite 330, Boston, MA 02111-1307 USA

Everyone is permitted to copy and distribute verbatim copies of this license document, but changing it is not allowed.

#### Preamble

The licenses for most software are designed to take away your freedom to share and change it. By contrast, the GNU General Public License is intended to guarantee your freedom to share and change free software–to make sure the software is free for all its users. This General Public License applies to most of the Free Software Foundation's software and to any other program whose authors commit to using it. (Some other Free Software Foundation software is covered by the GNU Library General Public License instead.) You can apply it to your programs, too.

When we speak of free software, we are referring to freedom, not price. Our General Public Licenses are designed to make sure that you have the freedom to distribute copies of free software (and charge for this service if you wish), that you receive source code or can get it if you want it, that you can change the software or use pieces of it in new free programs; and that you know you can do these things.

To protect your rights, we need to make restrictions that forbid anyone to deny you these rights or to ask you to surrender the rights. These restrictions translate to certain responsibilities for you if you distribute copies of the software, or if you modify it.

For example, if you distribute copies of such a program, whether gratis or for a fee, you must give the recipients all the rights that you have. You must make sure that they, too, receive or can get the source code. And you must show them these terms so they know their rights.

We protect your rights with two steps: (1) copyright the software, and (2) offer you this license which gives you legal permission to copy, distribute and/or modify the software.

Also, for each author's protection and ours, we want to make certain that everyone understands that there is no warranty for this free software. If the software is modified by someone else and passed on, we want its recipients to know that what they have is not the original, so that any problems introduced by others will not reflect on the original authors' reputations.

Finally, any free program is threatened constantly by software patents. We wish to avoid the danger that redistributors of a free program will individually obtain patent licenses, in effect making the program proprietary. To prevent this, we have made it clear that any patent must be licensed for everyone's free use or not licensed at all.

The precise terms and conditions for copying, distribution and modification follow.

### TERMS AND CONDITIONS FOR COPYING, DISTRIBUTION AND MODI-FICATION

**0.** This License applies to any program or other work which contains a notice placed by the copyright holder saying it may be distributed under the terms of this General Public License. The "Program", below, refers to

#### CONTENTS

any such program or work, and a "work based on the Program" means either the Program or any derivative work under copyright law: that is to say, a work containing the Program or a portion of it, either verbatim or with modifications and/or translated into another language. (Hereinafter, translation is included without limitation in the term "modification".) Each licensee is addressed as "you".

Activities other than copying, distribution and modification are not covered by this License; they are outside its scope. The act of running the Program is not restricted, and the output from the Program is covered only if its contents constitute a work based on the Program (independent of having been made by running the Program). Whether that is true depends on what the Program does.

**1.** You may copy and distribute verbatim copies of the Program's source code as you receive it, in any medium, provided that you conspicuously and appropriately publish on each copy an appropriate copyright notice and disclaimer of warranty; keep intact all the notices that refer to this License and to the absence of any warranty; and give any other recipients of the Program a copy of this License along with the Program.

You may charge a fee for the physical act of transferring a copy, and you may at your option offer warranty protection in exchange for a fee.

**2.** You may modify your copy or copies of the Program or any portion of it, thus forming a work based on the Program, and copy and distribute such modifications or work under the terms of Section 1 above, provided that you also meet all of these conditions:

a) You must cause the modified files to carry prominent notices stating that you changed the files and the date of any change. b) You must cause any work that you distribute or publish, that in whole or in part contains or is derived from the Program or any part thereof, to be licensed as a whole at no charge to all third parties under the terms of this License.

c) If the modified program normally reads commands interactively when run, you must cause it, when started running for such interactive use in the most ordinary way, to print or display an announcement including an appropriate copyright notice and a notice that there is no warranty (or else, saying that you provide a warranty) and that users may redistribute the program under these conditions, and telling the user how to view a copy of this License. (Exception: if the Program itself is interactive but does not normally print such an announcement, your work based on the Program is not required to print an announcement.)

These requirements apply to the modified work as a whole. If identifiable sections of that work are not derived from the Program, and can be reasonably considered independent and separate works in themselves, then this License, and its terms, do not apply to those sections when you distribute them as separate works. But when you distribute the same sections as part of a whole which is a work based on the Program, the distribution of the whole must be on the terms of this License, whose permissions for other licensees extend to the entire whole, and thus to each and every part regardless of who wrote it.

Thus, it is not the intent of this section to claim rights or contest your rights to work written entirely by you; rather, the intent is to exercise the right to control the distribution of derivative or collective works based on the Program.

In addition, mere aggregation of another work not based on the Program with the Program (or with a work based on the Program) on a volume of a storage or distribution medium does not bring the other work under the scope of this License.

**3.** You may copy and distribute the Program (or a work based on it, under Section 2) in object code or executable form under the terms of Sections 1 and 2 above provided that you also do one of the following:

a) Accompany it with the complete corresponding machine-readable source code, which must be distributed under the terms of Sections 1 and 2 above on a medium customarily used for software interchange; or,

**b**) Accompany it with a written offer, valid for at least three years, to give any third party, for a charge no more than your cost of physically performing source distribution, a complete machine-readable copy of the corresponding source code, to be distributed under the terms of Sections 1 and 2 above on a medium customarily used for software interchange; or,

c) Accompany it with the information you received as to the offer to distribute corresponding source code. (This alternative is allowed only for noncommercial distribution and only if you received the program in object code or executable form with such an offer, in accord with Subsection b above.)

The source code for a work means the preferred form of the work for making modifications to it. For an executable work, complete source code means all the source code for all modules it contains, plus any associated interface definition files, plus the scripts used to control compilation and installation of the executable. However,

as a special exception, the source code distributed need not include anything that is normally distributed (in either source or binary form) with the major components (compiler, kernel, and so on) of the operating system on which the executable runs, unless that component itself accompanies the executable.

If distribution of executable or object code is made by offering access to copy from a designated place, then offering equivalent access to copy the source code from the same place counts as distribution of the source code, even though third parties are not compelled to copy the source along with the object code.

4. You may not copy, modify, sublicense, or distribute the Program except as expressly provided under this License. Any attempt otherwise to copy, modify, sublicense or distribute the Program is void, and will automatically terminate your rights under this License. However, parties who have received copies, or rights, from you under this License will not have their licenses terminated so long as such parties remain in full compliance.

**5.** You are not required to accept this License, since you have not signed it. However, nothing else grants you permission to modify or distribute the Program or its derivative works. These actions are prohibited by law if you do not accept this License. Therefore, by modifying or distributing the Program (or any work based on the Program), you indicate your acceptance of this License to do so, and all its terms and conditions for copying, distributing or modifying the Program or works based on it.

**6.** Each time you redistribute the Program (or any work based on the Program), the recipient automatically receives a license from the original licensor to copy, distribute or modify the Program subject to these terms and conditions. You may not impose any further restrictions on the recipients' exercise of the rights granted herein. You are not responsible for enforcing compliance by third parties to this License.

7. If, as a consequence of a court judgment or allegation of patent infringement or for any other reason (not limited to patent issues), conditions are imposed on you (whether by court order, agreement or otherwise) that contradict the conditions of this License, they do not excuse you from the conditions of this License. If you cannot distribute so as to satisfy simultaneously your obligations under this License and any other pertinent obligations, then as a consequence you may not distribute the Program at all. For example, if a patent license would not permit royalty-free redistribution of the Program by all those who receive copies directly or indirectly through you, then the only way you could satisfy both it and this License would be to refrain entirely from distribution of the Program.

If any portion of this section is held invalid or unenforceable under any particular circumstance, the balance of the section is intended to apply and the section as a whole is intended to apply in other circumstances.

It is not the purpose of this section to induce you to infringe any patents or other property right claims or to contest validity of any such claims; this section has the sole purpose of protecting the integrity of the free software distribution system, which is implemented by public license practices. Many people have made generous contributions to the wide range of software distributed through that system in reliance on consistent application of that system; it is up to the author/donor to decide if he or she is willing to distribute software through any other system and a licensee cannot impose that choice.

This section is intended to make thoroughly clear what is believed to be a consequence of the rest of this License.

**8.** If the distribution and/or use of the Program is restricted in certain countries either by patents or by copyrighted interfaces, the original copyright holder who places the Program under this License may add an explicit geographical distribution limitation excluding those countries, so that distribution is permitted only in or among countries not thus excluded. In such case, this License incorporates the limitation as if written in the body of this License.

**9.** The Free Software Foundation may publish revised and/or new versions of the General Public License from time to time. Such new versions will be similar in spirit to the present version, but may differ in detail to address new problems or concerns.

Each version is given a distinguishing version number. If the Program specifies a version number of this License which applies to it and "any later version", you have the option of following the terms and conditions either of that version or of any later version published by the Free Software Foundation. If the Program does not specify a version number of this License, you may choose any version ever published by the Free Software Foundation.

**10.** If you wish to incorporate parts of the Program into other free programs whose distribution conditions are different, write to the author to ask for permission. For software which is copyrighted by the Free Software

Foundation, write to the Free Software Foundation; we sometimes make exceptions for this. Our decision will be guided by the two goals of preserving the free status of all derivatives of our free software and of promoting the sharing and reuse of software generally.

### **NO WARRANTY**

11. BECAUSE THE PROGRAM IS LICENSED FREE OF CHARGE, THERE IS NO WARRANTY FOR THE PROGRAM, TO THE EXTENT PERMITTED BY APPLICABLE LAW. EXCEPT WHEN OTHER-WISE STATED IN WRITING THE COPYRIGHT HOLDERS AND/OR OTHER PARTIES PROVIDE THE PROGRAM "AS IS" WITHOUT WARRANTY OF ANY KIND, EITHER EXPRESSED OR IMPLIED, IN-CLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FIT-NESS FOR A PARTICULAR PURPOSE. THE ENTIRE RISK AS TO THE QUALITY AND PERFOR-MANCE OF THE PROGRAM IS WITH YOU. SHOULD THE PROGRAM PROVE DEFECTIVE, YOU ASSUME THE COST OF ALL NECESSARY SERVICING, REPAIR OR CORRECTION.

12. IN NO EVENT UNLESS REQUIRED BY APPLICABLE LAW OR AGREED TO IN WRITING WILL ANY COPYRIGHT HOLDER, OR ANY OTHER PARTY WHO MAY MODIFY AND/OR REDIS-TRIBUTE THE PROGRAM AS PERMITTED ABOVE, BE LIABLE TO YOU FOR DAMAGES, INCLUD-ING ANY GENERAL, SPECIAL, INCIDENTAL OR CONSEQUENTIAL DAMAGES ARISING OUT OF THE USE OR INABILITY TO USE THE PROGRAM (INCLUDING BUT NOT LIMITED TO LOSS OF DATA OR DATA BEING RENDERED INACCURATE OR LOSSES SUSTAINED BY YOU OR THIRD PARTIES OR A FAILURE OF THE PROGRAM TO OPERATE WITH ANY OTHER PROGRAMS), EVEN IF SUCH HOLDER OR OTHER PARTY HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAM-AGES.

### Disclaimer

This is a voluntary work of an individual to develop a common platform for 8085 programming. Please be advised that nothing found here has necessarily been peer reviewed by people with the expertise required to provide you with complete, accurate or reliable information. So, user's discretion is advisable.

That is not to say that you will not always find inaccurate results in 8085 Simulator; but sometimes due to bug you may get some. However, the author cannot guarantee the validity or the liability of the results found using this software.

## **Product Description**

### **1.1 Motivation**

Understanding of Intel 8085 microprocessor is fundamental to getting insight into the Von-Neumann Architecture. It was first introduced in 1976, since then many generations of computer architecture have come up, some still persists while others are lost in history. This microprocessor still survives because it is still popular in university and training institutes to get students acquainted with basic computer architecture. For this purpose 8085 trainer kit are available on the market. However, with more popular technologies to learn, technical syllabus has very low time bandwidth available for this topic. All that is necessary for the students is to understand the functional working model of this basic architecture and then proceed on to next advance level of the subject.

With this academic learning purpose in mind this simulator software is designed. It helps in get started easily with example codes, and to learn the architecture playfully. It also provides a trainer kit as an appealing functional alternative to real hardware. The users can write assembly code easily and get results quickly without even having the actual hardware.

### **1.2 Installation and Upgrade Note**

The program code is written Java Syntax and available in java virtual machine executable format (.jar). To run in :

#### Windows :

1) Make sure you have Java installed on your system. Check this by typing **java -version** into the command terminal. If you don't have the latest version of Java, update it before proceeding.

2) Install Java (ver >6) http://www.java.com/en/download/manual.jsp

3) Just **double click** the ".jar" file, it should execute.

4) Otherwise you can execute in CMD ( Command Prompt ) by typing "java -jar <filename>.jar "

#### Linux :

1) Open terminal and type "java -jar <filename>.jar "

#### **UPDATES:**

Automatic or push updates are not supported in this software. Users are requested to keep track of the new release available at the web-link: https://8085simulator.codeplex.com/.

### **1.3 Limitations**

This or any 8085 simulator software is no way a replacement for real hardware. It only does functional simulation of the codes. It is not an emulator and hence do not expect that the timing information will be accurately modeled. However, the exact performance of the code can only be monitored in real 8085 microprocessor hardware.

### 1.4 Known Issues

- Issue 1 : DAA instruction wrongly toggles the carry flag if already there is a carry instead of setting it high, like take for example (88H + 88H). Users need to be cautious while using this instruction. It will be fixed in future realize v2.1.

- Issue 2: In Assembler Window, during pre-processing stage of the code it flags error if

; (SEMICOLON) comment marking character is followed after "//" (DOUBLE FORWARD SLASH).

Example → "<Label>: <Assembler Code> // <Comments> ; <More Comments>"

### **1.5** Software Design Architecture

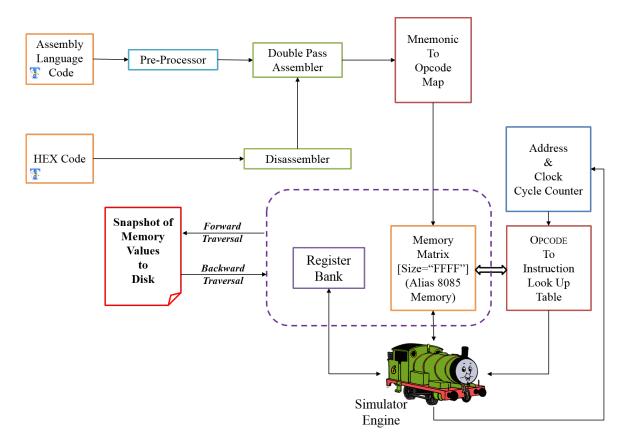

Figure 1.1: Software Architecture

#### 1.5.1 Preprocessor

Assembler directives are lines included in the code of programs preceded by a hash sign (#). These lines are not program statements but directives for the preprocessor. The preprocessor examines the code before actual assembling of code begins and resolves all these directives before any code is actually generated by regular statements.

#### 1.5.2 Assembler

It uses a 2 pass Assembler. In first pass it constructs *the symbol table* in which every label of the assembly program is stored with its corresponding location. In the second pass the assembler locates (using the flags array) and completes (using the symbol table) the partial mnemonics instructions. It then convert Mnemonic to Opcode using a mapping method.

#### **1.5.3** Simulator Engine

It resets all the register. Then starts from "Origin address". It scans the opcode value and sends it to "Opcode to instruction set look table". It then instructs the simulator engine the registers that will be affected, the number of data opcode that follows after the instruction opcode to increment the address and also to increment the number of clock cycles accordingly.

#### 1.5.4 Step-wise Traversal Controller

It consists of *memory snapshot maker* and *memory register - data value monitor*. During forward traversal *memory snapshot maker* dumps the entire memory current values to a temp file. With each forward step one temp file is created in the working directory pool of the software. During backward traversal the *memory snapshot maker* read backs the temp files and reloads with the past value. Once the process is stopped it clears out all the snapshots that are dumped. In this manner this software can able to traverse also in backward direction, inspite of using forward traversal instruction code.

### **1.6 Source Code**

The entire design is built in **Netbeans IDE** with JDK bundle. It can easily be opened by the software. The coding was done in bit unprofessional way, as it was developed during very early stage of my academics. Students are free to use the code for their understanding and distribution as defined under the GNU license agreement.

It is being actively maintained in GIT repository find it at link : https://8085simulator.codeplex.com/SourceControl/latest https://github.com/8085simulator/8085simulator

## Features

- 1. Assembler Editor

- Can load Programs written in other simulator

- Auto-correct and auto-indent features

- Supports assembler directives

- Number parameters can be given in binary, decimal and hexadecimal format

- Supports writing of comments

- Supports labeling of instructions, even in macros

- Has error checking facility

- Syntax Highlighting

- 2. Disassembler Editor

- Supports loading of Intel specific hex file format

- It can successfully reverse trace the original program from the assembly code, in most of the cases

- Syntax Highlighting and Auto Spacing

- 3. Assembler Workspace

- Contains the Address field, Label, Mnemonics, Hex-code, Mnemonic Size, M-Cycles and T-states

- Static Timing diagram of all instruction sets are supported

- Dynamic Timing diagram during step by step simulation

- It has error checking facility also

- 4. Memory Editor

- Can directly update data in a specified memory location

- It has 3 types of interface, user can choose from it according to his need.

- Show entire memory content

- Show only loaded memory location

- Store directly to specified memory location

- Allows user to choose memory range

- 5. I/O Editor

- It is necessary for peripheral interfacing.

- Enables direct editing of content

- 6. Interrupt Editor

- All possible interrupts are supported. Interrupts are triggered by pressing the appropriate column (INTR, TRAP, RST 7.5, RST 6.5, RST 5.5) on the interrupt table. The simulation can be reset any time by pressing the clear memory in the settings tab.

- 7. Debugger

- Support of breakpoints

- Step by step execution/debugging of program.

- It supports both forward and backward traversal of programs.

- Allows continuation of program from the breakpoint.

#### 8. Simulator

- There are 3 level of speed for simulation:

- Step-by-step → Automatic line by line execution with each line highlighting. The time to halt at each line is be decided by the user.

- Normal  $\longrightarrow$  Full execution with reflecting intermittent states periodically.

- Ultimate  $\longrightarrow$  Full execution with reflecting final state directly.

- There are 2 modes of simulator engine:

- Run all at a Time  $\longrightarrow$  It takes the current settings from the simulation speed level and starts execution accordingly.

- Step by Step → It is manual mode of control of FORWARD and BACKWARD traversal of instruction set. It also displays the in-line comment if available for currently executed instruction.

- Allows setting of starting address for the simulator

- Users can choose the mnemonic where program execution should terminate

- 9. Helper

- Help on the mnemonics is integrated

- CODE WIZARD is a tool added to enable users with very little knowledge of assembly code could also 8085 assembly programs.

- Already loaded with plenty SAMPLE programs

- Dynamic loading of user code if placed in user\_code folder

- It also includes a user manual

- 10. Printing

- Assembler Content

- Workspace Content

- 11. Register Bank  $\rightarrow$  Each register content is accompanied with its equivalent binary value

- Accumulator, Reg B, Reg C, Reg D, Reg E, Reg H, Reg L, Memory (M)

- Flag Register

- Stack Pointer (SP)

- Memory Pointer (HL)

- Program Status Word (PSW)

- Program Counter (PC)

- Clock Cycle Counter

- Instruction Counter

• Special blocks for monitoring Flag register and the usage of SIM and RIM instruction

#### 12. Crash Recovery

• Can recover programs lost due to sudden shutdown or crash of application

#### 13. 8085 TRAINER KIT

• It simulates the kit as if the user is working in the lab. It basically uses the same simulation engine at the back-end

#### 14. TOOLS

- Insert DELAY Subroutine TOOL

- It is a powerful wizard to generate delay subroutine with user defined delay using any sets of register for a particular operating frequency of 8085 microprocessor.

- Interrupt Service Subroutine TOOL

- It is a handy way to set memory values at corresponding vector interrupt address

- Number Conversion Tool

- It is a portable interconversion tool for Hexadecimal, decimal and binary numbers. So, that user do not need to open separate calculator for it.

# **Comparitive Analysis**

| Features                                                          | 8085 Simulator<br>version 2.0<br>(Jubin's) | Osonsoft 8085<br>simulator | GNUSim8085<br>simulator | Vaneet 8085<br>simulator | Abhijit's<br>8085<br>simulator |

|-------------------------------------------------------------------|--------------------------------------------|----------------------------|-------------------------|--------------------------|--------------------------------|

| Platform Independent                                              | *                                          |                            |                         |                          |                                |

| Backward Traversal Feature                                        | *                                          |                            |                         |                          |                                |

| 8085 Trainer Kit Simulation                                       | *                                          |                            |                         |                          | •                              |

| Backward Traversal Feature                                        | *                                          |                            |                         |                          |                                |

| Simulation speed control                                          | *                                          | •                          |                         |                          |                                |

| Number Conversion Tool                                            | *                                          |                            |                         |                          |                                |

| Setting of memory range,<br>stop mnemonic<br>and starting address | *                                          | *                          |                         |                          |                                |

| <b>Delay subroutine Insertion Tool</b>                            | *                                          |                            |                         |                          |                                |

| Crash recovery feature                                            | *                                          |                            |                         |                          |                                |

| Code Wizard                                                       | *                                          | *                          |                         |                          |                                |

Table 3.1: The Comparitive analysis between different softwares

$\bullet$ -Partial Support ;  $\bigstar$  – Full support

The table 3.1 compares the features that are special to this simulator. Apart from the contents listed most features are common, except for the peripheral attachment which will be added in future release.

# **Assembler Directives**

The assembler directives[1] are the instructions to the assembler concerning the program being assembled; they also are called *pseudo instructions* or *pseudo opcodes*.

In the Assembler Editor, the Assembler Directives **must be preceded by '.'** or **'#'**. The editor would then understand and would automatically change font foreground color to red color. Since execution of assembler directives do not assign any machine code but it directs the assembler engine and the memory loader to load a specific user code at user defined position. So it **loads code directly in the MEMORY EDITOR, it's output code is not visible in ASSEMBLER WORKSPACE**. Section 4.1 lists the assembler directives that are currently supported by the assembler.

### 4.1 Directives

|    | Assembler<br>Directives | Example            | Description                                                                                                                             |

|----|-------------------------|--------------------|-----------------------------------------------------------------------------------------------------------------------------------------|

| 1. | ORG<br>(Origin)         | # ORG C000H        | The next block of instruction should be stored<br>in memory locations starting at C000H                                                 |

| 2. | BEGIN<br>(Start)        | # BEGIN 2000H      | To start simulation from address 2000H                                                                                                  |

| 3. | END<br>(Stop)           | # END              | End of Assembly. It places the mnemonic defined at "Settings $\rightarrow$ Stop Simulation at Mnemonic"                                 |

| 4. | EQU<br>(Equal)          | # OUTBUF EQU 3945H | The value of the label OUTBUF is 3945H.<br>This may be used as memory location.                                                         |

| 5. | DB<br>(Define Byte)     | # DATA: DB F5H,12H | Initializes an area byte by byte, in successive memory locations<br>until all values are stored. Label DATA stores the initial address. |

| 6. | DW<br>(Define Word)     | # LABEL: DW 2050H  | Initializes an area two bytes at a time.                                                                                                |

| 7. | DS<br>(Define Storage)  | # STACK: DS 4      | Reserves a specified number of memory locations and set the initial address to label STACK.                                             |

### 4.2 Number Format Support

The Assembler for both code and assembler directive support flexible number entry mode

#### **Binary Number Entry Format**

- Digits should consists of 1's and 0's.

- The number of digits must be greater than 4, to prevent confusion with default Hexadecimal mode.

- The number must be followed by character 'b' or 'B', to indicate that it is a binary number. *Example:* To enter "F"(Hexadecimal Number) write it as 01111**B** or 01111**b**

#### **Decimal Number Entry Format**

- Digits should be within 0-9.

- The number of digits must be greater than 4, to prevent confusion with default Hexadecimal mode.

- The number must be followed by character 'd' or 'D', to indicate that it is a decimal number. *Example:* To enter "F"(Hexadecimal Number) write it as 0015**D** or 0015**d**

#### **Hexadecimal Number Entry Format**

- Digits should be within 0-9 and A-F.

- The number of digits can be of any size

- The number may be followed by character 'h' or 'H', to indicate that it is a hexadecimal number. *Example:* To enter "F"(Hexadecimal Number) write it as 0FH or 0Fh or just 0F

## Disassembler

A disassembler is a computer program that translates machine language into assembly language-the inverse operation to that of an assembler. A disassembler differs from a decompiler, which targets a high-level language rather than an assembly language. Disassembly, the output of a disassembler, is often formatted for human-readability rather than suitability for input to an assembler, making it principally a **reverse-engineering tool**.

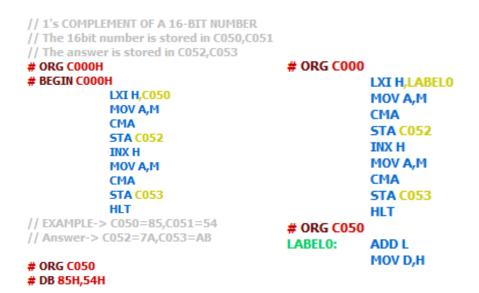

### 5.1 Disassembler Demonstration

Sub-figure (5.1a) shows a sample program i.e. "*1's COMPLEMENT OF A 16-BIT NUMBER*" loaded in the assembly language editor. It is then assembled by pressing the **Assemble** button. After assembling, memory content and assembler workspace are shown in sub-figure (5.1d) and sub-figure (5.1c) respectively. Then the **Hexcode** is saved by selecting "FILE $\rightarrow$ Save Hexcode" or presing "ALT+S".

The generated hexcode is now loaded in the Disassembler editor by selecting "FILE $\rightarrow$ Load Hexcode" or presing "ALT+O". As it can be seen in sub-figure (5.1e) the Intel Hex formatted code is syntactically highlighted. Now, press the **Disassemble**. If there is some error in the code that line will be highlighted in red. The tabbed window will not automatically change, even if there is no error. Now open the assembler editor the code is disassembled, as given in sub-figure (5.1b). Simultaneously the memory content is also loaded which is same as shown in sub-figure (5.1d). But, it is to be remembered that assembler workspace will remain empty, until the code is assembled from the assembler editor.

(a) Assembled Code

(b) Disassembled Code

|   |         |       |            |         |       |          |          | Memory Address | Value |

|---|---------|-------|------------|---------|-------|----------|----------|----------------|-------|

| * | Address | Label | Mnemonics  | Hexcode | Bytes | M-Cycles | T-States | C000           | 21    |

| V | C000    |       | LXI H,C050 | 21      | 3     | 3        | 10       | C001           | 50    |

|   | C001    |       |            | 50      |       |          |          | C002           | CO    |

|   | C002    |       |            | C0      |       |          |          | C003           | 7E    |

| 1 | C003    |       | MOV A,M    | 7E      | 1     | 2        | 7        | C004           | 2F    |

| 1 | C004    |       | СМА        | 2F      | 1     | 1        | 4        | C005           | 32    |

| 1 | C005    |       | STA C052   | 32      | 3     | 4        | 13       | C006           | 52    |

|   | C006    |       |            | 52      |       |          |          | C007           | CO    |

|   | C007    |       |            | C0      |       |          |          | C008           | 23    |

| √ | C008    |       | INX H      | 23      | 1     | 1        | 6        | C009           | 7E    |

|   | C009    |       | MOV A,M    | 7E      | 1     | 2        | 7        | COOA           | 2F    |

|   | COOA    |       | CMA        | 2F      | 1     | 1        | 4        | COOB           | 32    |

| - | COOR    |       |            | 32      |       |          | 13       | COOC           | 53    |

| • |         |       | STA C053   |         | 3     | 4        | 13       | COOD           | CO    |

|   | COOC    |       |            | 53      |       |          |          | COOE           | 76    |

|   | COOD    |       |            | C0      |       |          |          | C050           | 85    |

| V | COOE    |       | HLT        | 76      | 1     | 2        | 5        | C051           | 54    |

(c) Assembler Workspace after Assembling

(d) Memory Content after Assembling

(e) Hexcode of Assembled code

Figure 5.1: Showing working of Disassembler

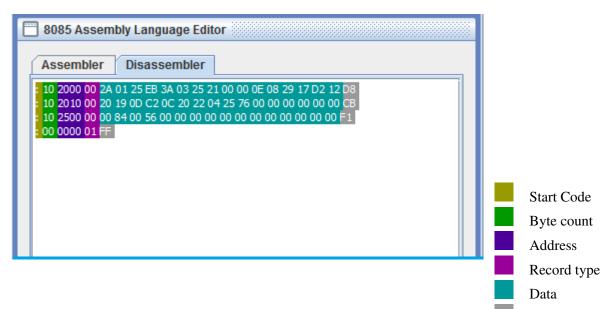

## 5.2 Intel HEX

Intel HEX[2] is a file format for conveying binary information for programming 8085 microprocessor. The assembler converts the program's assembly language code to machine code and outputs it into a HEX file. That file is then imported by a programmer to "burn" the machine code to the 8085 target system for loading and execution.

Figure 5.2: Intel HEX file format

Each line of Intel HEX fileconsists of six parts :

- Start code, one character, an ASCII colon ':'.

- **Byte count**, two hex digits, a number of bytes (hex digit pairs) in the data field. 16 (0x10) or 32 (0x20) bytes of data are the usual compromise values between line length and address overhead.

- Address, four hex digits, a 16-bit address of the beginning of the memory position for the data.

- **Record type**, two hex digits, 00 to 05, defining the type of the data field.

- 00, data record, contains data and 16-bit address.

- 01, End Of File record. Must occur exactly once per file in the last line of the file. The byte count is 00 and the data field is empty. Usually the address field is also 0000, in which case the complete line is ':00000001FF'.

- Data, a sequence of n bytes of the data themselves, represented by 2n hex digits.

- Checksum, two hex digits the least significant byte of the two's complement of the sum of the values of all fields except fields 1 and 6 (Start code ":" byte and two hex digits of the Checksum). It is calculated by adding together the hex-encoded bytes (hex digit pairs), then leaving only the least significant byte of the result, and making a 2's complement (either by subtracting the byte from 0x100, or inverting it by XOR-ing with 0xFF and adding 0x01). If you are not working with 8-bit variables, you must suppress the overflow by AND-ing the result with 0xFF. The overflow may occur since both 0x100-0 and (0x00 XOR 0xFF)+1 equal 0x100. If the checksum is correctly calculated, adding all the bytes (the Byte count, both bytes in Address, the Record type, each Data byte and the Checksum) together will always result in a value wherein the least significant byte is zero (0x00).

For example, on :0300300002337A1E

03 + 00 + 30 + 00 + 02 + 33 + 7A = E2, 2's complement is 1E

Checksum

### 5.3 Writing Hexcode in Disassembler

• **STEP 1:** To Enter the hexcode

| <start code=""><br/>:</start> | <byte count=""><br/>10</byte> | <address><br/>0000</address> | < <b>Record Type&gt;</b><br>00 | Ente<br>of data in | <b>Data&gt;</b><br>r 10 bytes<br>r Hexadecimal<br>ormat | < <b>Checksum&gt;</b><br><ctrl+space></ctrl+space> |

|-------------------------------|-------------------------------|------------------------------|--------------------------------|--------------------|---------------------------------------------------------|----------------------------------------------------|

| • STEP 2: To mark             | k end of file                 |                              |                                |                    |                                                         |                                                    |

| <start code=""><br/>:</start> | <byte count=""><br/>00</byte> | <address><br/>0000</address> | < <b>Record Type&gt;</b><br>01 | <data></data>      | <checksum><br/>FF</checksum>                            |                                                    |

#### TOOLS EMBEDDED IN DISASSEMBLER EDITOR

- AUTO CHECKSUM GENERATION Just press CTRL+SPACE at the end of each line it is auto calculated and appended to that line

- AUTO SYNTAX HIGHLIGHTING and FORMATING It is activated on pressing of ENTER key.

#### 5.3.1 Limitation of disassembler

- Cannot determine the begin address of execution

- Fails to distinguish between user defined data code and opcode, so it by default decode all as opcode.

# **Timing Diagram generator**

The 8085 Microprocessor is designed to execute 74 different types of instruction. Each instruction has two parts: OPCODE (operation code) and OPERAND. Each functions are divided into machine cycles and each cycles is further divided into T-states.

Basically, the microprocessor external communication functions can be divided into 3 categories of Machine Cycle:

- 1. Memory Read and Write

- 2. I/O Read and Write

- 3. Request Acknowledge

Of which Request Acknowledge machine cycle is not yet supported in this version of the software, but internally it is simulated.

There are three methods of Timing Diagram Generation :

- 1. Static Timing Diagram Generation

- 2. Dynamic Timing Diagram Generation

- (a) By Manual Step by Step Simulation

- (b) By Automatic Step by Step Simulation

### 6.1 Static Timing Diagram Generation

To open the Timing Diagram window click the filled rows of the column named "T-states" in the Assembler workspace, as shown in fig. 6.1. Static Timing Diagram is basically the machine cycles of the instruction in pre-simulation state. As, can be seen in fig. 6.2 where default values(00H in this case) are loaded during the Memory Read Cycle of "LDA 1234H" from address 1234H.

|   |             | sembler            | gs Simulation |         |       |           |          |   | Registers Memory     | Devices  |      |      |     |          |      |       |     |     |  |  |

|---|-------------|--------------------|---------------|---------|-------|-----------|----------|---|----------------------|----------|------|------|-----|----------|------|-------|-----|-----|--|--|

|   | Assemb      | ler                |               |         |       |           |          |   | Registers :          |          |      |      |     |          |      |       |     |     |  |  |

| * | Address     | Label              | Mnemonics     | Hexcode | Bytes | M-Cycles  | T-States |   | Register             | Value    | 7    | 6    | 5   | 4        | 3    | 2     | 1   | 0   |  |  |

| 1 | 0000        |                    | LXI H,1234    | 21      | 3     | 3         | 10       | • | Accumulator          | 00       | 0    | 0    | 0   | 0        | 0    | 0     | 0   | 0   |  |  |

|   | 0001        |                    |               | 34      |       |           |          |   | Register B           | 00       | 0    | 0    | 0   | 0        | 0    | 0     | 0   | 0   |  |  |

|   | 0002        |                    |               | 12      |       |           |          |   | Register C           | 00       | 0    | 0    | 0   | 0        | 0    | 0     | 0   | 0   |  |  |

| 1 | 0003        |                    | MVI B,67      | 06      | 2     | 2         | 7        |   | Register D           | 00       | 0    | 0    | 0   | 0        | 0    | 0     | 0   | 0   |  |  |

|   | 0004        |                    |               | 67      |       |           |          |   | Register E           | 00       | 0    | 0    | 0   | 0        | 0    | 0     | 0   | 0   |  |  |

| 1 | 0005        |                    | MOV M,B       | 70      | 1     | 2         | 7        |   | Register H           | 00       | 0    | 0    | 0   | 0        | 0    | 0     | 0   | 0   |  |  |

| 1 | 0006        |                    | LDA 1234      | 3A      | 3     | 4         | 13       |   | Register L           | 00       | 0    | 0    | 0   | 0        | 0    | 0     | 0   | 0   |  |  |

|   | 0007        |                    |               | 34      |       |           |          |   | Memory(M)            | 00       | 0    | 0    | 0   | 0        | 0    | 0     | 0   | 0   |  |  |

|   | 0008        |                    |               | 12      |       |           |          |   |                      |          |      |      |     |          |      |       | _   |     |  |  |

| 1 | 0009        |                    | HLT           | 76      | 1     | 2         | 5        |   | Resister             | Value    | S    | Ζ    | *   | AC       | *    | P     | *   | CY  |  |  |

|   |             |                    |               |         |       |           |          |   | Flag Resister        | 00       | 0    | 0    | 0   | 0        | 0    | 0     | 0   | 0   |  |  |

|   |             |                    |               |         |       |           |          |   | Typ                  | e        |      |      |     | V        | alue | 9     |     |     |  |  |

|   |             |                    |               |         |       |           |          |   | Stack Pointer(SP)    | -        | -    |      |     | 000      |      |       |     |     |  |  |

|   |             |                    |               |         |       |           |          |   | Memory Pointer (HL)  |          | -    |      |     | 000      | 0    |       |     |     |  |  |

|   |             |                    |               |         |       |           |          |   | Program Status Word  | (PSW)    | -    |      |     | 000      | 0    |       |     |     |  |  |

|   |             |                    |               |         |       |           |          |   | Program Counter(PC)  |          |      |      |     | 000      | 0    |       |     |     |  |  |

|   |             |                    |               |         |       |           |          |   | Clock Cycle Counter  |          | -    |      |     | 0        |      |       |     |     |  |  |

| _ |             |                    |               |         |       |           |          | • | Instruction Counter  |          |      |      |     | 0        |      |       |     |     |  |  |

|   |             |                    |               |         |       |           |          |   | SOD SID              | INTR TR  | ۵P   | P    | 7.5 |          | R6.5 |       | R5  | 5.5 |  |  |

| l | Simulat     | e                  | <u></u>       |         |       |           |          |   | 0 0                  | 0 0      |      |      | 0   | 1        | 0    |       | 0   |     |  |  |

| S | tart From - | → 000              | 0             |         |       |           |          |   |                      |          |      |      |     |          |      |       |     |     |  |  |

| - |             |                    |               |         |       |           |          |   | For SIM instruction  | SOD SDE  | *    | R7.  | 5 M | SE I     | M7.5 | M6    | 5 1 | M5. |  |  |

|   |             |                    |               |         |       |           |          |   |                      | 0 0      | 0    | 0    | (   | )        | 0    | 0     |     | 0   |  |  |

|   |             | <u>R</u> un all At | a Time        |         | Ste   | p By Step |          |   |                      | I        | _    |      |     |          |      |       | _   |     |  |  |

|   |             |                    |               |         |       |           |          |   | For RIM instruction  | SID 17.5 | 16.5 | 15.5 |     | EI       | M7.5 | M6    | 6 1 | ME  |  |  |

|   |             |                    |               |         |       |           |          |   |                      | 0 0      | 0.5  | 0    | _   | - I<br>) | 0    | 0     | 51  | 0   |  |  |

|   |             |                    |               |         |       |           |          |   | No. Converter Tool : |          |      |      |     |          |      |       |     |     |  |  |

|   |             |                    |               |         |       |           |          |   | Hexadecimal          | Deci     | mal  | -    |     |          | Bi   | inarv | -   | -   |  |  |

|   |             |                    |               |         |       |           |          |   |                      |          |      |      |     |          |      |       |     |     |  |  |

Figure 6.1: The Red box marks the area of the Assembler workspace to be clicked before execution of the program

|         |                                   | OPCODE FET      | TCH CYCLE |                | MEI                            | MORY READ CYCL  | .E        | MEI                            | MORY READ CYCL  | E         | ME                             | MORY READ CYCL  | _E        |

|---------|-----------------------------------|-----------------|-----------|----------------|--------------------------------|-----------------|-----------|--------------------------------|-----------------|-----------|--------------------------------|-----------------|-----------|

|         | T1                                | T2              | T3        | T4             | T1                             | T2              | T3        | T1                             | T2              | Т3        | T1                             | T2              | Т3        |

| CLK     |                                   |                 |           |                |                                |                 |           |                                |                 |           |                                |                 |           |

| A15-A8  | X 00                              | High-Order Memo | y Address | Unspecified    | 00                             | High-Order Memo | y Address | ) OO                           | High-Order Memo | y Address | 12                             | High-Order Memo | y Address |

| AD7-AD0 | ) 06 Low-Order<br>Mernory Address | {Opcode         | Read 3A > | Decodes Opcode | 07 Low-Order<br>Memory Address | {Opcode         | Read 34 > | 08 Low-Order<br>Memory Address | {Opcode         | Read 12 > | 34 Low-Order<br>Memory Address | {Opcode         | Read 00   |

| ALE     | ALE = 1                           | ALE = 0         |           |                | ALE = 1                        | ALE = 0         |           | ALE = 1                        | ALE = 0         |           | ALE = 1                        | ALE = 0         |           |

| 10 / M  |                                   | IO / M = 0      |           |                |                                | IO / M = 0      |           |                                | 10 / M = 0      |           |                                | 10 / M = 0      |           |

| S1      |                                   | S1 = 1          |           |                |                                | S1 = 1          |           |                                | S1 = 1          |           |                                | S1 = 1          |           |

| SO      |                                   | S0 = 1          |           |                |                                | S0 = 0          |           |                                | S0 = 0          |           |                                | S0 = 0          |           |

| RD      |                                   | RD = 0          |           |                |                                | RD = 0          |           |                                | RD = 0          |           |                                | RD = 0          |           |

| WR      |                                   | WR = 1          |           |                |                                | WR = 1          |           |                                | WR = 1          |           |                                | WR = 1          |           |

|         |                                   |                 |           |                |                                |                 |           |                                |                 |           |                                |                 |           |

**Figure 6.2:** Timing Diagram of "LDA 1234", where the last MEMORY READ CYCLE shows the value at address 1234H is set with default value 00H

### 6.2 Dynamic Timing Diagram Generation By Manual Step by Step Simulation

Dynamic Timing Diagram is the machine cycles of the instruction in real time simulation state. The stepping to the next instruction is controlled manually by the user, using "Step by Step" mode of execution. Here again as shown in fig. 6.3, need to click on the column named "T-states" of the currently highlighted row. Note carefully in fig. 6.4 that the values(67H in this case) are loaded in the Memory Read Cycle of "LDA 1234H" during reading of memory content at address 1234H.

|   | 085 Simulat |               | 1             |              |         |                | _         | _    |                                                                                                | _          |        |      |                |          |       |        |

|---|-------------|---------------|---------------|--------------|---------|----------------|-----------|------|------------------------------------------------------------------------------------------------|------------|--------|------|----------------|----------|-------|--------|

|   |             |               | gs Simulation | Subrouti     | ne Viev | w Load Sa      | ample Pro | gram |                                                                                                |            |        |      |                |          |       |        |

| E | ditor       | sembler       |               |              |         |                |           |      | Registers Memory                                                                               | Devices    |        |      |                |          |       |        |

| C | Assemb      | ler           |               |              |         |                |           |      | Registers :                                                                                    |            |        |      |                |          |       |        |

| * | Address     | Label         | Mnemonics     | Hexcode      | Bytes   | M-Cycles       | T-States  |      | Register                                                                                       | Value      | 7 6    | 5    | 4              | 3        | 2     | 1 0    |

| V | 0000        |               | LXI H,1234    | 21           | 3       | 3              | 10        |      | Accumulator                                                                                    | 67         | 0 1    |      |                | 0        |       | 1 1    |

|   | 0001        |               |               | 34           |         |                |           | E    | Register B                                                                                     | 67         | 0 1    |      |                | 0        | 1     | 1 1    |

|   | 0002        |               |               | 12           |         |                |           |      | Register C                                                                                     | 00         | 0 0    |      |                | 0        |       | 0 0    |

| 1 | 0003        |               | MVI B,67      | 06           | 2       | 2              | 7         | 1 1  | Register D                                                                                     | 00         | 0 0    | 0    | 0              | 0        | 0     | 0 0    |

|   | 0004        |               |               | 67           |         |                |           | 1 1  | Register E                                                                                     | 00         | 0 0    | 0    | 0              | 0        | 0     | 0 0    |

| 1 | 0005        |               | MOV M,B       | 70           | 1       | 2              | 7         |      | Register H                                                                                     | 12         | 0 0    | 0    | 1              | 0        | 0     | 1 0    |

| 1 | 0006        |               | LDA 1234      | 3A           | 3       | 4              | 13        |      | Register L                                                                                     | 34         | 0 0    | 1    | 1              | 0        | 1     | 0 0    |

|   | 0007        |               |               | 34           |         |                |           |      | Memory(M)                                                                                      | 67         | 0 1    | 1    | 0              | 0        | 1     | 1 1    |

|   | 0008        |               |               | 12           |         |                |           |      |                                                                                                |            |        |      |                |          |       |        |